(Revision of IEEE Std 824-1985)

# IEEE Standard for Series Capacitors in Power Systems

| Circuits and Devices              |

|-----------------------------------|

| Communications Technology         |

| Computer                          |

| Electromagnetics and<br>Radiation |

# **IEEE Power Engineering Society**

Sponsored by the IEEE Transmission and Distribution Committee

| Industrial Applications                            |

|----------------------------------------------------|

| $egin{array}{cccccccccccccccccccccccccccccccccccc$ |

| Stàpdards<br>Coordinating                          |

Published by the Institute of Electrical and Electronics Engineers, Inc., 345 East 47th Street, New York, NY 10017, USA.

July 18, 1994 SH17509

IEEE Std 824-1994 (Revision of IEEE Std 824-1985)

# IEEE Standard for Series Capacitors in Power Systems

Sponsor

Capacitor Subcommittee

of the

IEEE Transmission and Distribution Committee

Approved June 14, 1994

**IEEE Standards Board**

**Abstract:** Capacitors and assemblies of capacitors, insulation means, switching, protective equipment, and control accessories that form a complete bank for inserting in series with a transmission line are applied. Included are requirements for safety, rating, and protective device levels. Functional requirements for alarm devices, maintenance, design and production tests, and a guide for operation are included. Functional requirements for protective devices are addressed, including varistors and bypass gaps.

Keywords: bypass gap, force-triggered gap, self-triggered gap, series capacitor, trigger circuit

The Institute of Electrical and Electronics Engineers, Inc. 345 East 47th Street, New York, NY 10017-2394, USA

Copyright © 1994 by the Institute of Electrical and Electronics Engineers, Inc. All rights reserved. Published 1994. Printed in the United States of America.

ISBN 1-55937-441-1

No part of this publication may be reproduced in any form, in an electronic retrieval system or otherwise, without the prior written permission of the publisher.

IEEE Standards documents are developed within the Technical Committees of the IEEE Societies and the Standards Coordinating Committees of the IEEE Standards Board. Members of the committees serve voluntarily and without compensation. They are not necessarily members of the Institute. The standards developed within IEEE represent a consensus of the broad expertise on the subject within the Institute as well as those activities outside of IEEE that have expressed an interest in participating in the development of the standard.

Use of an IEEE Standard is wholly voluntary. The existence of an IEEE Standard does not imply that there are no other ways to produce, test, measure, purchase, market, or provide other goods and services related to the scope of the IEEE Standard. Furthermore, the viewpoint expressed at the time a standard is approved and issued is subject to change brought about through developments in the state of the art and comments received from users of the standard. Every IEEE Standard is subjected to review at least every five years for revision or reaffirmation. When a document is more than five years old and has not been reaffirmed, it is reasonable to conclude that its contents, although still of some value, do not wholly reflect the present state of the art. Users are cautioned to check to determine that they have the latest edition of any IEEE Standard.

Comments for revision of IEEE Standards are welcome from any interested party, regardless of membership affiliation with IEEE. Suggestions for changes in documents should be in the form of a proposed change of text, together with appropriate supporting comments.

Interpretations: Occasionally questions may arise regarding the meaning of portions of standards as they relate to specific applications. When the need for interpretations is brought to the attention of IEEE, the Institute will initiate action to prepare appropriate responses. Since IEEE Standards represent a consensus of all concerned interests, it is important to ensure that any interpretation has also received the concurrence of a balance of interests. For this reason IEEE and the members of its technical committees are not able to provide an instant response to interpretation requests except in those cases where the matter has previously received formal consideration.

Comments on standards and requests for interpretations should be addressed to:

Secretary, IEEE Standards Board 445 Hoes Lane P.O. Box 1331 Piscataway, NJ 08855-1331 USA

IEEE standards documents may involve the use of patented technology. Their approval by the Institute of Electrical and Electronics Engineers does not mean that using such technology for the purpose of conforming to such standards is authorized by the patent owner. It is the obligation of the user of such technology to obtain all necessary permissions.

# Introduction

(This introduction is not a part of IEEE Std 824-1994, IEEE Standard for Series Capacitors in Power Systems.)

This standard was revised in response to the advances made in series capacitor equipment and use of metal oxide in the protection systems for series capacitor banks. The principal objective of this standard is to provide a basis for uniformity in design and testing, and to assist users in the application of series capacitor equipment.

This standard was revised by a working group sponsored by the Capacitor Subcommittee of the Transmission and Distribution Committee of the IEEE Power Engineering Society.

At the time that this standard was approved, the Capacitor Subcommittee had the following membership:

# W. E. Reid, Chair

#### S. B. Ladd, Secretary

| I. Ares J. Barcus F. D. Barrow, Jr. B. Bhargava J. A. Bonner S. H. Cheng M. Chow H. E. Church C. R. Cusick | C. Ervin B. C. Furumasu J. E. Harder W. M. Hurst J. A. Lapoint J. Lapp A. Maguire J. Maneatis | A. S. Mehraban S. A. Miske, Jr. J. Nelson G. R. Newcomb* D. R. Ruthman J. Samuelsson R, Thallam K. K. Williams T. C. Wong |

|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

|------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

<sup>\*</sup>NEMA Member

The working group that developed this standard consisted of the following members:

| B. Bhargava  | S.B. Ladd    | A.S. Mehraban |

|--------------|--------------|---------------|

| C. R. Cusick | J.A. Lapoint | S.A. Miske    |

| M. Granger   | J. Lapp      | G.R. Newcomb* |

| S. Hertz     | J. Maneatis  | J. Samuelsson |

| W. M. Hurst  |              | R. Thallam    |

<sup>\*</sup>NEMA Member

The following persons were on the balloting committee:

| J. E. Applequist | J. G. Kappenman | R. J. Piwko      |

|------------------|-----------------|------------------|

| J. J. Burke      | G. G. Karady    | R. S. Prabhakara |

| V. L. Chartier   | N. Kolcio       | E. W. Reid       |

| C. C. Diemond    | T. J. McDermott | D. Reisinger     |

| D. A. Gilles     | F. D. Myers     | F. A. M. Rizk    |

| I. S. Grant      | D. L. Nickel    | B. R. Shperling  |

| W. S. Henry      | S. L. Nilsson   | J. Vithayathil   |

IEEE 824 94 ■ 4805702 0523776 T27 ■

When the IEEE Standards Board approved this standard on June 14, 1994, it had the following membership:

#### Wallace S. Read, Chair

# Donald C. Loughry, Vice Chair

# Andrew G. Salem, Secretary

Gilles A. Baril

Bruce B. Barrow

José A. Berrios de la Paz

Clyde R. Camp

James Costantino

Stephen L. Diamond

Donald C. Fleckenstein

Jay Forster\*

Ramiro Garcia

Donald N. Heirman Richard J. Holleman Jim Isaak Ben C. Johnson Sonny Kasturi Lorraine C. Kevra E. G. "Al" Kiener Ivor N. Knight Joseph L. Koepfinger\*

D. N. "Jim" Logothetis

L. Bruce McClung

Marco W. Migliaro

Mary Lou Padgett

Arthur K. Reilly

Ronald H. Reimer

Gary S. Robinson

Leonard L. Tripp

Also included are the following nonvoting IEEE Standards Board liaisons:

Satish K. Aggarwal James Beall Richard B. Engelman David E. Soffrin

Rachel A. Meisel

IEEE Standards Project Editor

<sup>\*</sup>Member Emeritus

# **Contents**

| CLAU | USE                                                  | PAGE     |

|------|------------------------------------------------------|----------|

| 1.   | Overview                                             | 1        |

|      | 1.1 Scope                                            | 1        |

| 2.   | References                                           | 1        |

| 3.   | Definitions                                          | 2        |

| 4.   | Service conditions                                   | 6        |

|      | 4.1 Normal service conditions                        | 6        |

|      | 4.2 Abnormal service conditions                      |          |

| 5.   | Rating                                               | 7        |

|      | 5.1 Basis of rating                                  | 7        |

|      | 5.2 Ambient temperature                              |          |

|      | 5.3 Rating information                               | 7        |

|      | 5.4 Current ratings                                  |          |

|      | 5.5 Fault current                                    | 8        |

|      | 5.6 Protective level                                 |          |

|      | 5.7 Insulation level                                 |          |

|      | 5.8 Capacitor impulse-voltage levels                 | 8        |

|      | 5.9 Electrical characteristics of capacitor bushings |          |

|      | 5.10 Varistor discharge energy                       |          |

|      | •                                                    |          |

| 6.   | Capacitor overvoltage protection                     | 11       |

|      | 6.1 General considerations                           | 11       |

|      | 6.2 Gap protection devices                           | 11       |

|      | 6.3 Protection using a varistor                      | 13       |

| 7.   | Protection and control                               | 14       |

|      | 7.1 Protection functions                             | 14       |

|      | 7.2 Control functions                                |          |

| 8.   | Testing                                              | 15       |

|      | 8.1 Capacitors                                       | 15       |

|      | 8.1 Capacitors                                       | 17       |

|      | 8.2 Capacitor ruse                                   |          |

|      | 8.4 Discharge current limiting device                |          |

|      |                                                      |          |

|      | 8.5 Bypass gap                                       | 21<br>29 |

|      |                                                      | 23<br>29 |

|      |                                                      | 2/       |

|      | 8.8 Apparatus insulators                             |          |

|      | 8.10 Control transformers                            |          |

|      | 0.10 Control transformers                            |          |

# IEEE 824 94 **= 4**805702 0523778 8TT **=**

| CLAU  | SE          |                                                     | PAGE |

|-------|-------------|-----------------------------------------------------|------|

| 9.    | Namepl      | ates and instruction books                          | 25   |

|       | 9.1 Na      | meplates                                            | 25   |

|       |             | truction books                                      |      |

|       | 9.3 Co      | lor                                                 | 26   |

| 10.   | Safety      |                                                     | 27   |

|       | 10.1 Per    | rsonnel protection                                  | 27   |

|       |             | scharge devices                                     |      |

|       |             | ounding provisions                                  |      |

|       | 10.4 Ha     | ndling and disposal                                 | 27   |

| ANNE  | XES         |                                                     |      |

| Annex | A Open      | rational guide and specification data (informative) | 28   |

|       | <b>A</b> .1 | Capacitor short-time capability                     | 28   |

|       | A.2         | Thermal stability                                   |      |

|       | A.3         | Internal partial discharge inception level          |      |

|       | A.4         |                                                     |      |

| Annex | B Maii      | ntenance and specification data (informative)       | 30   |

|       | <b>B</b> .1 | Inspection and maintenance                          | 30   |

|       | B.2         | Specification data                                  | 30   |

# IEEE Standard for Series Capacitors in Power Systems

#### 1. Overview

# 1.1 Scope

This standard applies to capacitors and assemblies of capacitors, insulation means, switching, protective equipment, and control accessories that form a complete bank for inserting in series with a transmission line. Included are requirements for safety, rating, and protective device levels. Functional requirements for alarm devices, maintenance, design and production tests, and a guide for operation are included. Functional requirements for protective devices are addressed, including varistors and bypass gaps.

#### 2. References

This standard shall be used in conjunction with the following publications:

ANSI C29.8-1985, American National Standard for Wet-Process Porcelain Insulators (Apparatus, Cap and Pin Type).<sup>1</sup>

ANSI C29.9-1983, American National Standard for Wet-Process Porcelain Insulators (Apparatus, Post Type).

ANSI C57.16-1958 (R 1971), American National Standard for Reactors, Requirements, Terminology and Test Code for Current Limiting Reactors (See Appendix, ANSI C57.99-1965).<sup>2</sup>

ANSI C93.3-1981, American National Standard for Requirements for Power Line Carrier Coupling Capacitors and Coupling Capacitor Voltage Transformers.

ANSI Z55.1-1967 (R 1973), American National Standard for Gray Finishes for Industrial Apparatus and Equipment.<sup>3</sup>

IEEE Std 4-1978, IEEE Standard Techniques for High Voltage Testing (ANSI).<sup>4</sup>

<sup>&</sup>lt;sup>1</sup>ANSI publications are available from the Sales Department, American National Standards Institute, 11 West 42nd Street, 13th Floor, New York, NY 10036, USA.

<sup>&</sup>lt;sup>2</sup>ANSI C57.16-1958 has been withdrawn; however, copies can be obtained from the Sales Department, American National Standards Institute, 11 West 42nd Street, 13th Floor, New York, NY 10036, USA.

<sup>&</sup>lt;sup>3</sup>ANSI Z55.1-1967 has been withdrawn; however, copies can be obtained from the Sales Department, American National Standards Institute, 11 West 42nd Street, 13th Floor, New York, NY 10036, USA.

<sup>&</sup>lt;sup>4</sup>IEEE publications are available from the Institute of Electrical and Electronics Engineers, 445 Hoes Lane, P.O. Box 1331, Piscataway, NJ 08855-1331, USA.

IEEE STANDARD FOR SERIES

IEEE Std 18-1992, IEEE Standard for Shunt Power Capacitors (ANSI).

IEEE Std 100-1992, The New IEEE Standard Dictionary of Electrical and Electronics Terms (ANSI).<sup>5</sup>

IEEE Std 1313-1993, IEEE Standard for Power Systems—Insulation Coordination (Formerly ANSI C92.1-1987) (ANSI).

IEEE Std C37.09-1979 (Reaff 1988), IEEE Standard Test Procedure for AC High-Voltage Breakers Rated on a Symmetrical Current Basis (ANSI).

IEEE Std C57.12.00-1993, IEEE Standard General Requirements for Liquid-Immersed Distribution, Power, and Regulating Transformers (ANSI).

IEEE Std C57.13-1993, IEEE Standard Requirements for Instrument Transformers.

IEEE Std C57.19.00-1991, IEEE Standard General Requirements and Test Procedure for Outdoor Power Apparatus Bushings (ANSI).

IEEE Std. C62.11-1993 IEEE Standard for Metal-Oxide Surge Arresters for Alternating Current Power Circuits (ANSI).

NEMA LA1-1992, Surge Arresters.<sup>6</sup>

#### 3. Definitions

The definitions used in this standard can be found in IEEE Std 100-1992. In some instances, the definition in IEEE Std 100-1992 may be either too broad or too restrictive. In such a case, an additional definition or note has been included.

- 3.1 ambient temperature: The temperature of the medium such as air, gas, or water, into which the heat of the equipment is dissipated.

- **3.2 bypass current:** The current flowing through the bypass switch, protective device, or other devices, in parallel with the series capacitor.

- 3.3 bypass gap: A gap, or systems of gaps, to protect either the capacitor against overvoltage or the varistor against thermal overload, by carrying load or fault current around the protected equipment for some specified time. The bypass gap normally consists of a power gap and a trigger circuit.

- **3.4 bypass interlocking device:** A device that requires all three phases of the switch to be in the same open or closed position.

- **3.5 bypass switch:** A device such as a switch or circuit breaker used in parallel with a series capacitor and its protective device to shunt line current for some specified time or continuously. This device may also have the capability of inserting and bypassing the capacitor into a circuit carrying a specified level of current.

<sup>&</sup>lt;sup>5</sup>IEEE Std 100-1992 states that wave shape designation is measured in microseconds (μs). To avoid confusion, in this standard where other units of measurement are necessary, units ns, μs, or ms are shown after all wave shape designations.

<sup>&</sup>lt;sup>6</sup>NEMA publications are available from the National Electrical Manufacturers Association, 2101 L Street NW, Washington, DC 20037, USA.

<sup>&</sup>lt;sup>7</sup>Information on references can be found in clause 2.

- **3.6 capacitor:** An assembly of one or more capacitor elements in a single container, with one or more insulated terminals brought out.

- 3.7 capacitor bus: The main conductors that serve to connect the capacitor assemblies in series with the line.

- **3.8 capacitor element:** The smallest unit of a capacitor consisting of metallic foil plates separated by a dielectric film made typically of a polymer, paper, or combination of the two materials.

- 3.9 capacitor fuse: A capacitor fuse that provides an externally visible indication of fuse operation.

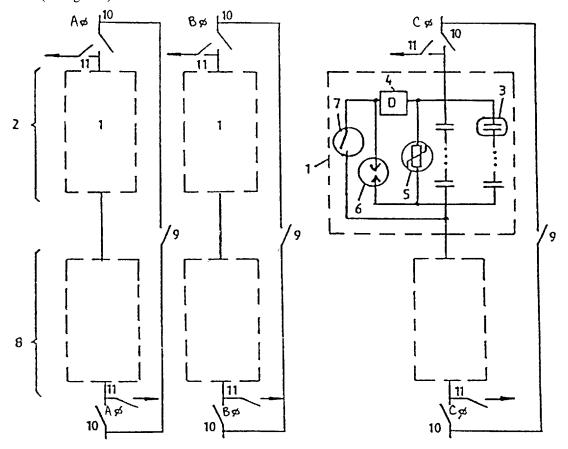

- **3.10 capacitor group:** An assembly of more than one capacitor connected in parallel between two buses or terminals (see figure 1).

- 1—Capacitor segment (1 ø)

- 2—Capacitor switching step/Capacitor module (3 ø)

- 3—Capacitor group

- 4—Discharge current limiting damping device

- 5—Varistor

- 6—Bypass gap

- 7-Bypass switch

- 8—Additional switching steps when required

- 9-External bypass disconnect switch

- 10-External isolating disconnect switch

- 11-External grounding disconnect switch

Figure 1—Typical series capacitor bank nomenclature

IEEE STANDARD FOR SERIES

- **3.11 capacitor platform:** A structure that supports the capacitor rack assemblies and all associated equipment and protective devices, and is supported on insulators compatible with line-to-ground insulation requirements.

- **3.12 capacitor rack:** A frame that supports one or more capacitors.

- **3.13 capacitor segment:** A single-phase assembly of groups of capacitors that has its own voltage-limiting device and relays to protect the capacitors from overvoltages and overloads (see figure 1).

- **3.14 capacitor switching step:** A three-phase function that consists of one or more capacitor segments per phase with capacitor bypass devices connected in parallel control devices, and provision for interlocked operation of the single-phase or three-phase switches when bypassing or inserting the capacitor segments (see figure 1). This is sometimes referred to as a capacitor module.

- **3.15 capacitance unbalance detection function:** The detection of objectionable unbalance in capacitance between capacitor groups within a phase, such as that caused by blown capacitor fuses or faulted capacitors, and to initiate an alarm, the closing of the capacitor bypass switch, or both.

- **3.16 discharge current limiting device:** A reactor or equivalent device to limit the current magnitude and frequency of the discharge of the capacitors during closing operations of the bypass switch or gap (see figure 1).

- **3.17 discharge device:** An internal or external device permanently connected in parallel with the terminals of a capacitor for the purpose of reducing the residual voltage after the capacitor is disconnected from an energized line.

- **3.18 external line fault:** A fault that occurs on lines or equipment other than the transmission line that includes the series capacitor installation.

- **3.19 forced-triggered gap:** A bypass gap that is designed to operate on external command on quantities such as varistor energy, current magnitude, or rate of change of such quantities. The sparkover of the gap is initiated by a trigger circuit. After initiation, an arc is established in the power gap. Forced—triggered gaps typically sparkover only during internal faults.

- 3.20 fused capacitor: A capacitor in combination with a fuse, either external or internal to the case.

- **3.21 insertion:** The opening of the capacitor bypass device to place the series capacitor in service with or without load current flowing.

- **3.22 insertion current:** The steady state root-mean-square current that flows through the series capacitor after the bypass device has opened.

- **3.23 insertion voltage:** The steady state root-mean-square voltage appearing across the series capacitor upon the interruption of the bypass current with the opening of the bypass device.

- **3.24 insulation level:** The combination of power frequency and impulse test voltage values that characterize the insulation of the capacitor bank with regard to its capability of withstanding the electric stresses between platform and earth, or between platform-mounted equipment and the platform.

- 3.25 internal line fault: A fault that occurs on the transmission line section that includes the series capacitor installation.

CAPACITORS IN POWER SYSTEMS

- **3.26 lockout protection function:** A function that blocks the opening of the bypass switch and prevents insertion of the switching steps, following the closure of the bypass switch from a cause that warrants inspection or maintenance.

- **3.27 loss of control power protection:** A means to initiate the closing of the bypass device upon the loss of normal control power.

- **3.28 overload detection:** A means to detect excessive overload of series capacitor bank components and to initiate an alarm signal, the closing of the associated bypass switch, or both.

- **3.29 platform control power:** Energy source(s) available at platform potential for performing protection and control functions.

- **3.30 platform fault-detection:** A means used to detect insulation failure on the platform that results in current flowing from normal current-carrying circuit elements to the platform.

- **3.31 platform-to-ground signaling devices:** Devices to transmit protection, control, and alarm functions to and from the platform.

- 3.32 power gap: The part of the bypass gap that carries the fault current after sparkover of the bypass gap.

- **3.33 protective device:** A bypass gap, varistor, or other device that limits the voltage on the capacitor segment to a predetermined level when overcurrent flows through the series capacitor (that is, during system faults, system swings, or other abnormal events), and that is capable of carrying capacitor discharge, system fault, and load current for the specified duration.

- **3.34 protective level of the bypass gap:** The maximum instantaneous voltage (including tolerance) appearing across the capacitor immediately before or during operation of the bypass gap.

- **3.35 protective level of the varistor:** The maximum instantaneous voltage appearing across the capacitor at a specified current through the varistor.

- 3.36 reinsertion: The restoration of load current to the series capacitor from the bypass path (see figure 1).

- 3.37 reinsertion current: The transient current, load current, or both, flowing through the series capacitor after the opening of the bypass path.

- **3.38 reinsertion voltage:** The transient voltage, steady-state voltage, or both, appearing across the series capacitor after the opening of the bypass path.

- **3.39 self-triggered gap:** A bypass gap that is designed to sparkover on the voltage that appears across the gap terminals. The sparkover of the gap is normally initiated by a trigger circuit set at a specified voltage level. A self-triggered bypass gap may be used for the primary protection of the capacitor. The self-triggered gap may sparkover during external as well as internal faults.

- **3.40 series capacitor:** A device that has the primary purpose of introducing capacitive reactance in series with an electric circuit.

- **3.41 series capacitor bank:** An assembly of capacitors and associated auxiliaries, such as structures, support insulators, switches, and protective devices, with control equipment required for a complete operating installation.

- **3.42 subharmonic detector:** A device that detects subharmonic current of specified frequency and duration and initiates an alarm signal or corrective action.

**IEEE STANDARD FOR SERIES**

- **3.43 sustained bypass current detection:** A means to detect prolonged current flow through the protective device and to initiate closing of the bypass switch.

- **3.44 sustained overvoltage detection device:** A device that detects capacitor voltage above rating but below the operation level of the protective device and initiates an alarm signal or corrective action.

- **3.45 trigger circuit:** The part of the bypass gap that initiates the sparkover of the bypass gap at a specified voltage level or by external command.

- 3.46 valve element: A single nonlinear resistor disc used in a surge arrester or varistor unit.

- **3.47 varistor:** An assembly of varistor units that limit overvoltages to a given value. In the context of series capacitors, the varistor is typically defined by its ability to divert fault current around a series capacitor, limiting the voltage to a specified protective level while absorbing energy. The varistor is designed to withstand the temporary overvoltages and continuous operating voltage across the series capacitor.

- **3.48 varistor unit:** A single insulated enclosure containing one or more valve elements in series and possibly in parallel.

# 4. Service conditions

NOTE-For additional information on service conditions, see annex A.

#### 4.1 Normal service conditions

Series capacitor banks shall be suitable for operation at their specified current, voltage, and frequency ratings under the following conditions:

- a) The altitude does not exceed 3300 ft (1000 m) above sea level.

- b) The ambient temperature is within the limits specified in 5.2. (Capacitors may be exposed to the direct rays of the sun.)

- c) The ice load does not exceed 0.75 in (19 mm).

- d) Rated frequency, rated continuous current, and short time overload current for durations are as specified on nameplate and instruction book.

- e) Wind velocities are no greater than 80 mph (128 km/h).

- f) The vibration of any directly connected equipment and the shock caused by the operation or maintenance of the equipment does not shorten the service life.

- g) The horizontal seismic acceleration of the equipment does not exceed 0.2 g and the vertical acceleration does not exceed 66% of the horizontal acceleration when applied simultaneously.

Equipment furnished as an integral part of this apparatus shall meet the electrical, mechanical, and thermal requirements of the series capacitors with which it is used.

# 4.2 Abnormal service conditions

The application of series capacitor banks at other than the normal service conditions shall be considered as special and should be brought to the attention of the manufacturer. Examples of such conditions are as follows:

- a) Service conditions other than those listed in 4.1

- b) Exposure to excessively abrasive and conducting dust

- c) Exposure to salt, damaging fumes, or vapors

- d) Unusual transportation or storage conditions

- e) Conditions requiring overinsulation or extra creepage on insulators

# 5. Rating

## 5.1 Basis of rating

The capacitive reactance of a series capacitor bank per phase shall be specified at its nominal operating frequency and at a uniform case with internal dielectric temperature of 25 °C. The tolerance shall be  $\pm 2.5\%$ .

# 5.2 Ambient temperature

The capacitor bank shall be designed for continuous operation and short-time overloads in an outdoor environment with unrestricted ventilation, no wind, and direct sunlight under the ambient temperatures given in table 1. Where ambient air temperatures higher than those given in table 1 or lower than -40 °C are expected in service, the manufacturer should be consulted.

Table 1—Maximum ambient

| Manuskins                             | Ambient air temperature (°C) |                            |  |

|---------------------------------------|------------------------------|----------------------------|--|

| Mounting arrangement                  | 24 hour average <sup>a</sup> | Normal annual <sup>b</sup> |  |

| Isolated capacitor                    | 46                           | 35                         |  |

| Single row of capacitors              | 46                           | 35                         |  |

| Multiple rows and tiers of capacitors | 40                           | 25                         |  |

| Metal-enclosed or housed equipment    | 40                           | 25                         |  |

<sup>&</sup>lt;sup>a</sup>The 24 h arithmetic average of hourly readings during the hottest day at that location.

# 5.3 Rating information

Rating information should be determined for each specific application and should include the following classifications:

- a) Rated continuous current. The root-mean-square (rms) current that the capacitor or capacitor bank shall be capable of carrying continuously at rated frequency and rated ambient temperature range.

- b) Rated voltage. The rms voltage appearing across the capacitor bank-rated reactance with rated current flowing.

- c) Rated frequency. The frequency (measured in Hz) of the circuit for which the capacitor bank is designed.

- d) Capacitance. The capacitance (measured in μF) with the case and dielectric at a temperature of 25 °C, that will yield rated reactance at rated frequency. Capacitance change over the ambient temperature range shall be within a 10% range.

- e) Reactance. The capacitive reactance (L) of the capacitor bank in one phase as determined from rated capacitance and rated frequency. Rated reactance will result in rated voltage appearing across the capacitor bank with rated current flowing.

- f) Kilovar rating. The kilovar rating as determined from rated reactance, and rated current per phase (multiply by 3 for total three-phase bank kilovar).

<sup>&</sup>lt;sup>b</sup>As defined in the reports of the United States Weather Bureau.

# 5.4 Current ratings

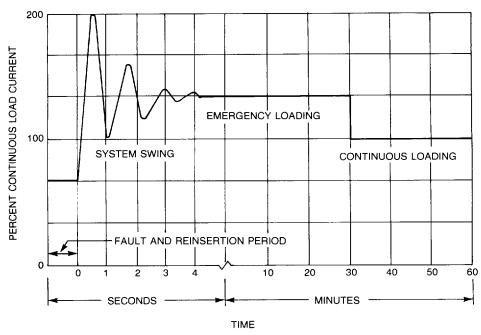

The series capacitor bank shall be capable of withstanding the rated continuous current, system swing, and emergency loading as specified by the purchaser in the general form illustrated in figure 2.

Figure 2—Typical time-current profile on reinsertion of capacitor bank (after fault and loss of parallel line)

#### 5.5 Fault current

The series capacitor bank shall be capable of withstanding the system fault current specified by the purchaser when following occurs:

- a) The capacitor is not bypassed.

- b) The capacitor is bypassed.

#### 5.6 Protective level

The series capacitor bank shall be capable of withstanding the voltage levels of the protective device specified by the purchaser.

#### 5.7 Insulation level

The series capacitor bank shall meet the insulation level from platform-to-ground as specified in table 4.

# 5.8 Capacitor impulse-voltage levels

The capacitors shall withstand the impulse levels in table 2 as demonstrated by the tests specified in 8.1.1.7.

CAPACITORS IN POWER SYSTEMS

# 5.9 Electrical characteristics of capacitor bushings

The capacitor bushings shall be designed to meet the requirements of table 3.

Table 2—Impulse levels (+)a

| Range of capacitor voltage ratings<br>(terminal-to-terminal)<br>(V, rms) | Impulse level (1.2/50)<br>(terminal-to-case)<br>(kV peak) |

|--------------------------------------------------------------------------|-----------------------------------------------------------|

| 216–1199                                                                 | 30 <sup>b</sup>                                           |

| 1200–5000                                                                | 75                                                        |

| 5001–15 000                                                              | 95                                                        |

| 13 200–25 000                                                            | 125                                                       |

<sup>&</sup>lt;sup>a</sup>See 8.1.1.7.

Table 3—Electrical characteristics of bushings

|                                                                             |                                                              | Withstand test voltage             |                                   |                                                             |

|-----------------------------------------------------------------------------|--------------------------------------------------------------|------------------------------------|-----------------------------------|-------------------------------------------------------------|

| Range of capacitor<br>voltage ratings<br>(terminal-to-terminal)<br>(V, rms) | Minimum insulation<br>Creepage Distance<br>(in) <sup>a</sup> | 60 Hz<br>dry<br>1 min<br>(kV, rms) | 60 Hz<br>wet<br>10 s<br>(kV, rms) | Impulse<br>1.2/50<br>(or 1.5/40)<br>full wave<br>(kV crest) |

| 216–1199                                                                    | 2 (5.08 cm)                                                  | 10                                 | 6                                 | 30 <sup>b</sup>                                             |

| 1200–5000                                                                   | 5.5 (13.97 cm)                                               | 27                                 | 24                                | 75                                                          |

| 5001–15 000                                                                 | 10 (25.40)                                                   | 35                                 | 30                                | 95                                                          |

| 13 200–25 000                                                               | 16 (40.64 cm)                                                | 42                                 | 36                                | 125                                                         |

| 15 000–25 000                                                               | 17 (43.18 cm)                                                | 60                                 | 50                                | 150                                                         |

| 19 920–25 000                                                               | 26 (66.04 cm)                                                | 80                                 | 75                                | 200                                                         |

<sup>&</sup>lt;sup>a</sup>At elevations higher than 3300 ft (1000 m) above sea level or in contaminated environments, additional insulation may be required to prevent bushing flashovers or excessive leakage current.

NOTE—Withstand test voltages are for standard temperature and humidity at sea level.

<sup>&</sup>lt;sup>b</sup>Not applicable to 216 V-1199 V indoor capacitors.

<sup>&</sup>lt;sup>b</sup>Not applicable to indoor ratings.

Table 4—Dielectric test voltages platform-to-ground insulation

| 60 Hz withstand                 |               | Withstand     |                              |                                     |

|---------------------------------|---------------|---------------|------------------------------|-------------------------------------|

| System voltage rating (kV, rms) | Dry (kV, rms) | Wet (kV, rms) | BIL <sup>a</sup> (kV, crest) | Wet BSL <sup>b</sup><br>(kV, crest) |

| Col 1                           | Col 2         | Col 3         | Col 4                        | Col 5                               |

| 34.5                            | 95            | 80            | 200                          |                                     |

| 46.0                            | 120           | 100           | 250                          | _                                   |

| 69.0                            | 175           | 145           | 350                          |                                     |

| 115.0                           | 280           | 230           | 550                          | <u> </u>                            |

| 138.0                           | 335           | 275           | 650                          |                                     |

| 161.0                           | 385           | 315           | 750                          |                                     |

| 230.0                           | 545           | 455           | 1050                         | 750                                 |

| 298.0                           | 610           | 525           | 1300                         | 900                                 |

| 345.0                           | 710           | 620           | 1550                         | 1050                                |

| 500.0                           | 810           | 710           | 1800                         | 1175                                |

| 700.0                           | 940           | 830           | 2050                         | 1300                                |

<sup>&</sup>lt;sup>a</sup>Basic impulse insulation level

# 5.10 Varistor discharge energy

The varistor shall be capable of absorbing energy associated with power system event(s), which may be identified by the purchaser as a duty cycle, without thermal runaway or mechanical failure. These events are typically associated with system internal or external faults, but can include operation at emergency overload ratings or during system swings.

bWet withstand switching-surge voltage level

NOTE—For voltage classes 345 kV and above, tests shall be performed on a completely assembled platform. Previous design tests may satisfy this requirement.

CAPACITORS IN POWER SYSTEMS

# 6. Capacitor overvoltage protection

# 6.1 General considerations

During normal service operation, series capacitors are subject to transient swing currents and fault currents that result in transient voltage stresses across the capacitors and to platform equipment. The magnitude and duration of voltage stresses are essential parameters in series capacitor bank design. If the voltage stress and duration are not controlled, an uneconomical bank design, based on these short-time transient stresses, could result.

Bypass gaps and varistors used alone or in combination are normally used in parallel with the series capacitor to control the magnitude and duration of capacitor overvoltages. The method of overvoltage protection selected should take into consideration a number of factors that include transient swing current and overload current ratings, operating practices, maintenance, reinsertion capability, fault magnitude, fault duty cycle, and economics.

The bypass gap protects the capacitor by collapsing the voltage across the capacitor and providing a path for current around the capacitor. Power gaps can be designed to operate on voltage magnitude across the gap or be induced to fire by a triggering circuit. Generally, the trigger circuit uses quantities such as varistor energy, current magnitude, and rate of change of quantities, to determine gap operation. Power gaps need to be deionized after operation to restore dielectric strength to allow reinsertion of the capacitor bank.

The varistor is a voltage-dependent nonlinear resistor that protects by limiting (clamping) voltage across its terminals to a designed protective level by diverting excess fault current. The varistor does not require any deionization time after a protection or voltage limiting action; therefore, reinsertion of capacitors into the circuit is immediate.

The bypass gap and varistor both need to be protected from excess duty. For gaps, this is generally excessive conduction time measured in cycles. For varistors, the measure is typically energy.

Generally, capacitor overvoltages and varistor energies resulting from fault currents are critical to the design of the protection equipment. The following is a list of parameters that should be considered when reviewing these stresses:

- a) Bank location

- b) Fault location—Internal vs. external

- c) Fault type—Single-phase and multiphase

- d) Fault duration—Fault scenarios, including automatic and manual reclosing times, and breaker times

- e) Post-fault conditions—Swing current and half hour overload

- f) Back-up fault clearing scenarios

- g) Reinsertion voltages—(gap systems) under post-fault conditions

#### 6.2 Gap protection devices

# 6.2.1 Gap overvoltage protection

A bypass gap can be designed to operate with sustained or unsustained arcs. The sustained arc gap (non-self-extinguishing gap) requires bypassing or current interruption by other devices to extinguish the arc. The unsustained arc gap (self-extinguishing gap) has the ability to extinguish the arc itself, by magnetic or pneumatic action. The unsustained arc gap may cause greater stress on capacitors and other equipment.

Sparkover of a bypass gap is often initiated by a trigger circuit.

An untriggered bypass gap, that is, a bypass gap without a trigger circuit, is very seldom used for series capacitor protection application, due to its sensitivity to variations in ambient conditions as well as gap wear. This causes large variations in sparkover voltage, that is, large tolerances and gives unreliable operation.

A triggered bypass gap can be designed to operate on voltage (self-triggered gap) or on command based on other quantities, such as varistor energy, current magnitude, or rate of change of quantities (forced-triggered gap).

A forced-triggered gap may be used in combination with a varistor for varistor-protected series capacitors.

#### 6.2.2 Self-triggered gap

The bypass gap is normally set to such a level that sparkover will occur for internal faults. The gap may or may not sparkover for external faults, depending on power system requirements.

For an internal fault cleared by the primary line protection, the gap should, after arc extinction, recover dielectrically within the interval before line breaker autoreclosing.

For an external fault, after sparkover followed by arc extinction resulting from closure of a bypass switch, the gap should recover dielectrically so that the capacitor can be reinserted by the opening of the bypass switch shortly after the external fault has been cleared. If fast capacitor reinsertion is required, two self-triggered gaps with different settings and an additional switch can be used to obtain this function (dual gap system). The same function may be achieved by forced arc extinguishing of the power gap.

Selection of the gap setting should consider the need for capacitor reinsertion during specified power system postfault conditions.

The gap shall be able to withstand the specified fault current for the specified duration. In case of high-speed reclosing of line breakers, the gap shall be designed to withstand consecutive sparkovers that may result as a consequence of unsuccessful high-speed reclosing, while maintaining the protective level to within the specified tolerance.

If the series capacitor comprises multiple segments, due regard shall be taken to the dc component in the reinsertion voltage, when the gap setting is determined.

When the bypass gap sparks over, the capacitor will discharge from the sparkover voltage level through a loop circuit that normally consists of the bypass gap, capacitor fuses, and current-limiting reactor. In the case where the bank bypass switch closes, the capacitor voltage prior to closing will be the product of the load current and capacitive reactance.

The reactor size is chosen to limit the current, considering each of the components in the loop circuit for both switch and bypass gap operations. The current-limiting damping equipment normally comprises a reactor with inherent damping and a parallel-connected resistor, if required.

# 6.2.3 Forced-triggered gap

A forced-triggered gap may be used in combination with a varistor to limit the varistor energy under certain fault conditions. It shall operate only on command.

For an internal fault, the gap may be permitted to sparkover on command and bypass the varistor and the capacitor. The gap should recover dielectrically within the dead interval before the line breaker reclosures.

#### CAPACITORS IN POWER SYSTEMS

For an external fault, the gap shall normally not operate. The capacitor voltage is limited to a specified protection level by the varistor. Capacitor reinsertion is obtained automatically and without delay upon clearing of the fault by the line breakers.

The design of the varistor/gap combination shall be designed to work correctly during specified power system swing and emergency loading conditions.

As in the case of a self-triggered gap, the forced-triggered gap shall withstand specified fault current for specified durations, repeated sparkovers at nonsuccessful reclosings, and capacitor discharge current superimposed on the power frequency fault current.

# 6.3 Protection using a varistor

A varistor limits the temporary overvoltage across the capacitors by conducting the excess transmission line current, usually due to faults, that would otherwise cause excessive capacitor voltage. This condition occurs on each half cycle during the overcurrent condition or until the parallel bypass switch closes or the bypass gap fires. The maximum voltage that results across the series capacitor is dependent upon the nonlinear voltage-current characteristics of the varistor and the magnitude of the overcurrent. Because the varistor voltage increases with current, the maximum protective level is usually defined at the maximum expected varistor current during a power system fault. Energy is absorbed by the varistor during conduction. The selection of the varistor energy capability and protection of the varistor against overstress are important aspects of the series capacitor protection system.

The selection of the protective level of the varistor shall take into account the voltage associated with the various nonfault currents through the series capacitor for normal, emergency, and system swing conditions. The varistor shall typically be capable of withstanding these voltages following the absorption of fault energy and with the most unfavorable ambient temperature.

The voltage associated with the power system swing is often the highest nonfault voltage that the series capacitor and the varistor must withstand. As such, it can be the determining factor in establishing the protective level. A low varistor protective level may mean the varistor will exhibit significant conduction and energy absorption during the swing, necessitating a varistor with a greater energy rating. Varistor energy absorption can be reduced by increasing the protective level of the varistor. However, the capacitor design is subject to change because of the higher overvoltages.

The choice of protective level can also be influenced by its relationship to the varistor energy requirements for external faults. Typically, a lower protective level increases varistor energy absorption. Conversely, a higher protective level requires less energy absorption. These factors, plus the preference of the purchaser and other power system considerations, are included in the choice of protective level. Another power system consideration is subsynchronous resonance. The voltage magnitude of large subsynchronous oscillations is limited by the varistor. In applications where subsynchronous oscillations are a concern, there is a preference for a lower protective level.

The varistor is designed with power current and energy absorption capabilities that shall be consistent with anticipated power system fault conditions. In addition to the protective level, critical factors determining varistor requirements are the equivalent impedance of the power system, the duration of the fault, and transmission line breaker reclosure sequence. With this information, the varistor current and energy absorption can be determined.

On complicated power systems, computer simulations are needed to adequately determine varistor duty. Typically, the varistor will be designed to withstand the current and energy associated with specified external line section faults so that the series capacitor in the unfaulted line remains in service during the fault and the critical post-fault period to enhance power system stability.

Internal line section faults near the series capacitor bank can cause much higher varistor current and energy. This is especially true if the installation is located at the end of the line near a substation with a high short-circuit current. In this case, the series capacitor protection system typically incorporates a parallel gap to bypass the series capacitor at high speed for a close-in fault. The bypass gap greatly reduces the energy requirements for the varistor. However, the varistor shall withstand the high fault current until bypass occurs.

In such applications, the speed of the bypass is an important factor in the varistor design. If the installation is located out on the transmission line, the varistor duty for a fault near a bank is substantially less than the end of the line application (but far more than for the external fault). This makes the speed of the bypass less important. It becomes more practical to omit a parallel bypass gap and to limit the duration of varistor conduction for a fault by closing the bypass switch.

# 7. Protection and control

#### 7.1 Protection functions

This function only covers the protective functions relating to the protection of the series capacitor equipment located on the platform. Phase-to-ground and multiple-phase faults occurring in the capacitor bank will be recognized by transmission line relays located elsewhere. The following protection functions, as a minimum, should be considered.

- a) Limiting of maximum capacitor voltage to a predetermined level

- b) Limiting the profiles of sustained overcurrent to specific levels and times (see figure 2)

- c) Limiting of duration of current through the protective gap

- Detection of capacitance unbalance due to fuse operation or faulted capacitor for a predetermined limit

- e) Detection of equipment-to-platform faults

- f) Loss of control power

- g) Varistor protections and failure detection

- h) Platform-to-ground signal failure

- i) Bypass switch pole discordance protection

## 7.2 Control functions

The following control functions may be considered:

- a) Reinsertion of capacitor after protective device operation with or without delay as specified

- b) Bypass or insertion of capacitor from ground level by control means

- c) Interlocking between segments of same switching step

- d) Bypass or insertion of capacitor in response to predetermined load conditions

- e) Lockout control for predetermined protection

- f) Indication and alarm contacts as required by customer's specifications

# 8. Testing

Tests are designated as either design tests or production tests.

- a) Design tests. Design tests shall be performed by the manufacturer to demonstrate compliance of the design with specific requirements. However, when design tests have been performed on equipment of similar design and the manufacturer can supply reports of such tests acceptable to the purchaser, design tests may be waived by mutual agreement between the manufacturer and purchaser.

- b) Production tests. Production tests shall be performed by the manufacturer on each component.

# 8.1 Capacitors

# 8.1.1 Design tests

## 8.1.1.1 Capacitance change vs. temperature test

Test data shall be provided to verify that the capacitance change over the ambient temperature range is within 10% as specified in 5.2.

#### 8.1.1.2 Thermal stability test

Testing shall be performed in accordance with IEEE Std 18-1992, except that all references to voltage should be changed to current and references to capacitance should be changed to reactance. This test may be waived if a similar unit has passed this test. The thermal density of the tested unit shall be at least as high as that of the design to be qualified.

# 8.1.1.3 Radio influence voltage test

Tests on capacitor shall be performed in accordance with the requirements given IEEE Std 18-1992. (The major insulation, that is line-to-ground tests, shall be made according to 8.8.)

#### 8.1.1.4 Discharge test

The capacitor shall be tested at approximately 25 °C by charging to a dc voltage of 110% of the protective level and discharged through a circuit that limits the first peak of discharge current to not less than 120% of the current that flows when the capacitor is bypassed by the protective device or bypass switch. The damping of the capacitor discharge shall be such that the capacitor voltage and current at the end of the third half cycle of the oscillation shall be equal to or greater than that which will occur in the actual application. Three samples shall each be tested 25 times at intervals of less than 2 min. After this test, the capacitor shall be tested at approximately 25° C by charging to a dc voltage equal to 110% of the maximum protective level and the discharged twice through a circuit having an impedance as low as possible. The capacitance should be rechecked after the test, to determine if there is any adverse change.

#### 8.1.1.5 Voltage decay test

The capacitor should be charged to a dc voltage equal to 1.1 times 1.41 times rated rms voltage and then isolated for 5 min. The resulting residual voltage on this capacitor should not exceed 50 V.

#### 8.1.1.6 Terminal-to-terminal dielectric test

Tests shall be performed in accordance with 8.1.2.1.

IEEE STANDARD FOR SERIES

#### 8.1.1.7 Terminal-to-case test

Tests shall be performed in accordance with the requirements given in IEEE Std 18-1992 and 8.1.2.

# 8.1.1.8 Impulse withstand test

Tests shall be performed in accordance with the requirements given in IEEE Std 18-1992, subclause 7.7.

### 8.1.1.9 Capacitor bushings test

Tests shall be performed in accordance with the requirements given in IEEE Std 18-1992, subclause 7.8.

#### 8.1.2 Production tests

#### 8.1.2.1 Terminal-to-terminal dielectric test

Capacitors protected by an overvoltage protective device shall withstand a dc test voltage equal to 120% of the crest value of the maximum specified rms protective level. Direct current test voltage shall be no less than 4.3 times rated rms voltage. If the device protects more than one series group, the test voltage shall be prorated accordingly to determine the test voltage to be applied to each capacitor. This test shall be applied at a capacitor case and internal temperature of 25 °C  $\pm$  5 °C for a period of 10 s. The capacitance shall be measured on each unit both before and after the application of the test voltage.

The initial capacitance measurement shall be at low voltage. The change in capacitance, as a result of the test voltage, shall be less than either a value of 2% or that caused by failure of a single capacitor element of the particular design.

#### 8.1.2.2 Terminal-to-case dielectric test

Testing will be performed in accordance with the requirements given in IEEE Std 18-1992, subclause 7.2.2.

#### 8.1.2.3 Capacitance tests

Capacitance measurements shall be performed on each capacitor to demonstrate that its operating kilovar will be within ±5% of the kilovar rating of the capacitor when operated at the rated current and frequency, and with a case and internal temperature of 25 °C. Measurements made at other than 25 °C shall be adjusted, using a curve applicable to the type of capacitor being tested.

#### 8.1.2.4 Leak test

A suitable test shall be made on each capacitor to ensure that it is free from leaks.

# 8.1.2.5 Discharge resistor tests

Testing shall be performed in accordance with the requirements given in IEEE Std 18-1992, subclause 7.5.

#### 8.1.2.6 Loss determination tests

Testing shall be performed in accordance with IEEE Std 18-1992, subclause 7.6.

#### 8.1.2.7 Capacitance tests on multi-unit rack assemblies

Capacitance measurements shall be made to ensure that its value is within  $\pm 2.5\%$  of rating, and its measured value shall be stamped on the nameplate.

# 8.2 Capacitor fuse

#### 8.2.1 Design tests

# 8.2.1.1 Discharge test

The capacitor fuse shall be tested to confirm that it will withstand the capacitor discharges associated with gap sparkover or bypass breaker closure. The discharge shall have a peak current,  $I^2t$  and frequency of greater than 110% of that required by the application.

Five sample fuses shall each be subjected to 250 discharges. Cooling between discharges is permissible. In addition, each fuse shall be subjected to 2 discharges within a 0.5 s period. The two discharge sequence shall be repeated 25 times with cooling between sequences.

The fuses shall be evaluated by measuring their voltage drop before and after the discharge testing. The latter test shall be made after the fuses have returned to the initial temperature. The voltage drop will be measured with a direct current in the fuse of 10% of its rms continuous current rating. The change in the voltage drop resulting from the discharge testing shall be less than 10%.

#### 8.2.1.2 Interruption test

The capacitor fuse shall be tested to demonstrate that it will interrupt the fault and discharge current into a faulted capacitor from the parallel unfaulted capacitors and withstand the associated recovery voltage. The test shall reflect the magnitude and frequency of the current and the fuse recovery voltage of the actual installation. The interruption shall occur without bursting and without external damage to the fuse at the voltage and parallel stored energy associated with the maximum protective device setting.

#### 8.2.2 Production tests

As a minimum, the fuse shall be inspected and the fuse resistance shall be measured, and be within manufacturer's specified tolerance.

#### 8.3 Varistor

Some of the following tests are the same as or similar to those described in IEEE Std C62.11-1993.

The testing procedures described below do not cover special applications such as under oil varistor units. In cases of abnormal service conditions, the test procedures and levels are subject to agreement between the manufacturer and the purchaser.

#### 8.3.1 Design tests

# 8.3.1.1 Accelerated aging procedure

Tests shall be performed on individual valve elements to ensure that the varistor, when continuously operated at the voltage associated with 1.1 times rated bank current, will not result in degradation of varistor performance beyond specified limits as agreed to between purchaser and manufacturer over the service life of the equipment. Testing shall be in accordance with subclause 8.5 of IEEE Std C62.11-1993. The determined voltage rations  $K_c$  and  $K_R$  are then to be used in the thermal recovery test (see 8.3.1.3.2).

IEEE STANDARD FOR SERIES

#### 8.3.1.2 Discharge-voltage test

This test shall be performed to confirm that, when the completed varistor is operating under specified line fault condition, it will limit the voltage to its required protective level. Discharge voltage shall be measured for a discharge current having a virtual front time of 100–200 µs.

NOTE—This front time is to account for current commutation from the capacitor during a power system fault. Calculations and field tests have shown that the current commutation from the capacitor to the varistor results in a current rise in the varistor that is faster than that resulting from a power frequency applied voltage. The magnitude of the discharge current shall be the maximum system fault current that could flow in the number of columns represented by the test samples.

# 8.3.1.3 Energy absorption and thermal recovery test

Tests shall be performed to demonstrate that the varistor can withstand the energy associated with specified fault and operating conditions and still show thermal recovery.

# 8.3.1.3.1 Energy absorption test

The energy absorption test shall be performed on a minimum of three test samples with at least two valve elements in series in open air at 20 °C  $\pm$  5 °C.

The test shall be performed, separately or all together, on the same number of parallel columns that are used in one housing of the varistor. The test energy shall correspond to the most severe of the line fault conditions specified (decisive case). This energy is then scaled down (prorated) with respect to rating and number of parallel columns and series valve elements of the actual test samples compared to the complete varistor.

Since the energy capability of a varistor depends somewhat on the current density (amplitude or equivalent pulse duration), the test has to demonstrate the worst-case conditions. The test shall be made 20 times with the application of power frequency voltage with the same duration as or shorter than the decisive case. For shorter durations the power frequency voltage can be replaced by a single impulse (rectangular or sinusoidal wave) of the maximum current amplitude. The test energy shall be increased to account for the given current sharing tolerances. This is done by multiplying test energy with the maximum specified current sharing ratio divided by the actual current sharing ratio of each test sample. If the tests are performed on single-column test samples, the actual current sharing ratio is always one. Full cooling to ambient temperature between each energy application is permitted.

The voltage-current characteristics shall be checked at a current corresponding to the maximum fault current, prior to and after the energy absorption test and shall not result in a voltage change of more than  $\pm 3\%$ . The valve elements shall exhibit no significant physical damage, such as cracks.

#### 8.3.1.3.2 Thermal recovery test

A test shall be performed on three thermally prorated sections to demonstrate that the varistor can absorb the total energy from either the line fault conditions or combinations of such injections as specified by the purchaser, and withstand the subsequent associated operating conditions, which include the overvoltage due to the swing current, followed by the voltage due to the 30-minute emergency overload current, followed by the continuous rated capacitor voltage of the bank (see IEEE Std C62.11-1993 for thermal prorating requirements). Prior to testing, the prorated sections shall be preheated to  $60 \, ^{\circ}\text{C} \pm 5 \, ^{\circ}\text{C}$ .

<sup>&</sup>lt;sup>8</sup>60 °C accounts for 40 °C ambient, solar heating, no wind, plus self heating

Within 5 min after removing the heat source, the scaled down (prorated) energy discharge should be applied. Within 1 min after the energy discharge the specified temporary overvoltage sequence, followed by the 30 min emergency overload voltage, should be applied.

After this emergency overload, the continuous-rated capacitor voltage shall be applied for 30 min to verify thermal stability. During these last 30 min, valve element temperature, resistive component of current, and/or power dissipations shall be monitored until the measured value is appreciably reduced (success) or a thermal runaway condition is evident (failure). The test shall occur in still air with an ambient temperature between 20 °C and 60 °C.

#### 8.3.1.4 Pressure relief tests

In the event of a varistor failure, the current through the varistor unit will typically be a combination of capacitor discharge current and power frequency fault current. Procedure to verify the varistor pressure relief capability under conditions of varistor failure shall be agreed to by manufacturer and purchaser. In the absence of an alternative procedure, pressure relief tests with both high and low current shall be performed according to the procedure described in IEEE Std C62.11-1993, subclause 8.9 for station class arresters.

The high-current test should be performed with a power fault current equal to or greater than the worst power frequency fault current associated with a particular application.

#### 8.3.2 Production (routine) tests

# 8.3.2.1 Energy absorption

The valve elements shall be tested for energy absorption as agreed upon between the manufacturer and the purchaser.

#### 8.3.2.2 Current sharing

Current sharing measurements shall be performed on all parallel-connected valve element columns of the varistor for each segment, to verify that the maximum current sharing tolerances between columns are within the limit established for the design. Measurements shall be made such that the average test current per column is of a magnitude equal to the average current per column, which would occur in the entire varistor during system fault conditions, imparting maximum energy into the varistor. The testing can be made in either two ways:

- All parallel columns are tested simultaneously with measurements taken of the current through each column.

- b) The discharge voltage at the average test current per column shall be measured for all columns. After this discharge voltage measurement the columns showing the highest and lowest discharge voltage shall be tested simultaneously with measurements of the current recorded. If the voltage measurement method is adopted the relative measuring accuracy must be within ±0.3%.

#### 8.3.2.3 Protective level

Measurements shall be made in order to confirm that the varistor meets its guaranteed protective level at a discharge current magnitude corresponding to the maximum complete varistor current during rated fault conditions. The measurements can be made either on single valve elements and added up, or on complete varistor units.

#### 8.3.2.4 Verification of low-current characteristics

Measurement of watts loss or reference voltage of each varistor unit shall be made to verify the continuous and emergency overload capability of the varistor. The reference voltage is the lowest peak value independent of polarity of power frequency voltage, divided by the square root of two, and measured at the reference current. The reference current is the peak value of the resistive component of a power frequency current used to determine the reference voltage of the varistor unit. The reference current shall be high enough to make effects of stray capacitances negligible and shall be specified by the manufacturer. Typically this is in the range of 0.05 to 1.0 mA per square centimeter of disc area.

#### 8.3.2.5 Ionization voltage test

Measurement of radio influence voltage (RIV) or internal corona (picocoulomb) of each varistor unit shall be made at a voltage corresponding to the 30-minute emergency overload condition. The value shall be in accordance with NEMA LA1-1992 or agreed upon between the manufacturer and purchaser.

#### 8.3.2.6 Seal integrity test

A test shall be made of the atmospheric sealing system of each varistor unit in accordance with IEEE Std C62.11-1993.

# 8.4 Discharge current limiting device

#### 8.4.1 Design tests

If a current limiting reactor is used as a discharge current limiting device, it shall meet applicable sections of ANSI C57.16-1958.

#### 8.4.1.1 Discharge test

The discharge current limiting device shall be subjected to a test current not less than 1.1 times the maximum total transient bypass branch discharge current. The transient bypass branch current shall be the combined system fault current and capacitor discharge current that is calculated at maximum gap setting and specified power frequency fault current including offset. The discharge test may be carried out with a test current comprising a half cycle current wave of power frequency and with the same amplitude. The test should be repeated 25 times without evidence of mechanical or electrical damage.

#### 8.4.1.2 Fault current test

The discharge current limiting device shall be tested to demonstrate that it will carry its rated power frequency fault current (including peak asymmetrical) for its rated duration without evidence of excessive temperature, or mechanical or electrical damage, according to ANSI C57.16-1958, section 5.3.5.

#### 8.4.1.3 Temperature rise

The test shall be made according to ANSI C57.16-1958, section 5.3.2, mounting the discharge current limiting device similarly to that used in service. Apply rated continuous power frequency current and measure temperature conditions for the length of time required to reach stable thermal conditions and establish temperature rise above 40 °C ambient. The temperature rise should not exceed the manufacturer's established limit for the materials used.

#### 8.4.1.4 Inductance

The test shall be made according to ANSI C57.16-1958, section 5.3.1 to demonstrate that inductance of the discharge current limiting device agrees with its rated value.

# 8.4.2 Production tests

Production tests shall be performed according to ANSI C57.16-1958.

# 8.5 Bypass gap

#### 8.5.1 Self-triggered gap

#### 8.5.1.1 Design tests

The following design tests shall be carried out. If the trigger circuit is not affected by the discharge and power frequency fault currents, it can be omitted in the tests.

#### 8.5.1.1.1 Discharge current test

The power gap shall be subjected to a test current not less than 1.1 times the maximum total transient bypass branch discharge current. The transient bypass branch current shall be the combined system fault and capacitor discharge current that is calculated at maximum gap setting and specified power frequency fault current including offset.

The discharge test may be carried out with a test current comprising a one-half cycle current wave of power frequency and with the same amplitude.

The test shall be repeated 25 times without mechanical damage, excessive erosion, or greater than 10% change in sparkover voltage of the power gap corrected to standard atmosphere conditions.

#### 8.5.1.1.2 Fault current test

The power gap shall be tested 25 times to demonstrate that it will carry its specified power frequency fault current for specified primary clearing time duration without evidence of excessive erosion or greater than 10% change in sparkover voltage of the power gap corrected to standard atmosphere conditions.

#### 8.5.1.1.3 Recovery voltage test

A test shall be performed to demonstrate that the bypass gap recovers sufficient dielectric strength after conducting specified fault current for a specified duration followed by a recovery period and recovery voltage specified by the user.

The reinsertion voltage level shall be mutually agreed upon by the manufacturer and user. A typical value is 80–90% of the protective level voltage. For practical reasons, by agreement, the test may be carried out on the power gap and the trigger circuit separately. The test shall take into account the differences in the relative air density between the test conditions and the worst-case field conditions.

# 8.5.1.1.4 Sparkover test

The trigger circuit shall be subjected to a sparkover test to demonstrate that the trigger circuit sparks over correctly at the correct voltage level and recovers to the specified recovery voltage level within the specified time interval.

IEEE STANDARD FOR SERIES

#### 8.5.1.1.5 Overall bypass gap test

A design test shall be carried out to verify that the bypass gap comprising the power gap and the trigger circuit operates correctly during normal, emergency, and fault conditions. Considerations shall be taken for possible variation in sparkover voltage of the power gaps due to environmental factors and possible electrode rescission, determined in 8.5.1.1.1 and 8.5.1.1.2. Oscillographic recordings shall be made.

#### 8.5.1.1.6 Ambient environmental test

The trigger circuit shall be subjected to an ambient environmental test to demonstrate that it operates correctly within the specified tolerances, for specified variations in the environmental factors, such as temperature and air pressure. If the triggering function is independent of environmental factors, this test does not apply.

#### 8.5.1.2 Production tests

The following production tests shall be made:

- a) Verification that the components used are of the proper ratings

- b) Adjustment and checking of power and trigger gaps for proper sparkover setting

#### 8.5.2 Forced-triggered gap

# 8.5.2.1 Design tests

The following design tests shall be carried out. If the trigger circuit is not affected by the discharge and power frequency fault currents, it can be omitted in tests described in 8.5.2.1.1 to 8.5.2.1.3.

# 8.5.2.1.1 Discharge current test

The power gap shall be subjected to a test current not less than 1.1 the maximum total transient bypass branch discharge current. The transient bypass branch current shall be calculated at maximum protective varistor level and at specified power frequency fault current. The power frequency fault current will typically not include offset because of the effect of the varistor. The discharge test may be carried out with a test current comprising of one-half cycle current wave of power frequency and with the same amplitude.

The test shall be repeated 10 times without mechanical damage, excessive erosion, or greater than 10% change in sparkover voltage of the power gap corrected to standard atmospheric conditions.

#### 8.5.2.1.2 Fault current test

The power gap shall be tested 10 times to demonstrate that it will carry its specified power frequency fault current for its specified primary clearing time duration without evidence of excessive erosion and greater than 10% change in sparkover of the power gap corrected to standard atmospheric conditions.

#### 8.5.2.1.3 Recovery voltage test

The test shall be performed to demonstrate that the bypass gap recovers sufficient dielectric strength after conducting specified fault current for specified duration followed by a recovery period and recovery voltage specified by the user. The recovery period is typically the dead time of line reclosing.

A typical recovery voltage level is the protective level of the varistor. The test should take into account the differences in the relative air density between the test conditions and worst-field conditions. For practical

#### CAPACITORS IN POWER SYSTEMS

reasons, by agreement the test may be carried out on the power gap and the trigger circuit separately. The test shall be carried out once.

#### 8.5.2.1.4 Overall bypass gap test

The bypass gap comprising the power gap and the trigger circuit, together with a capacitor and a varistor, shall be subjected to a design test to verify that the bypass gap operates correctly during normal, emergency, and fault conditions. The gap shall only sparkover when ordered to do so. Consideration shall be taken to possible variation in sparkover voltage of the power gaps due to environmental factors and possible erosion determined in 8.5.2.1.1 and 8.5.2.1.2. Oscillographic recordings should be made.

#### 8.5.2.2 Production tests

The following production tests shall be made: